Our Vision

Making formal normal

We are always a foot away from an electronic chip. Whether it is a mobile phone, a laptop, a smartwatch, a car, or a plane – semiconductors are driving the world. Our reliance on electronic chips powered by semiconductor integrated circuit (IC) designs, and the underlying software has never been more profound.

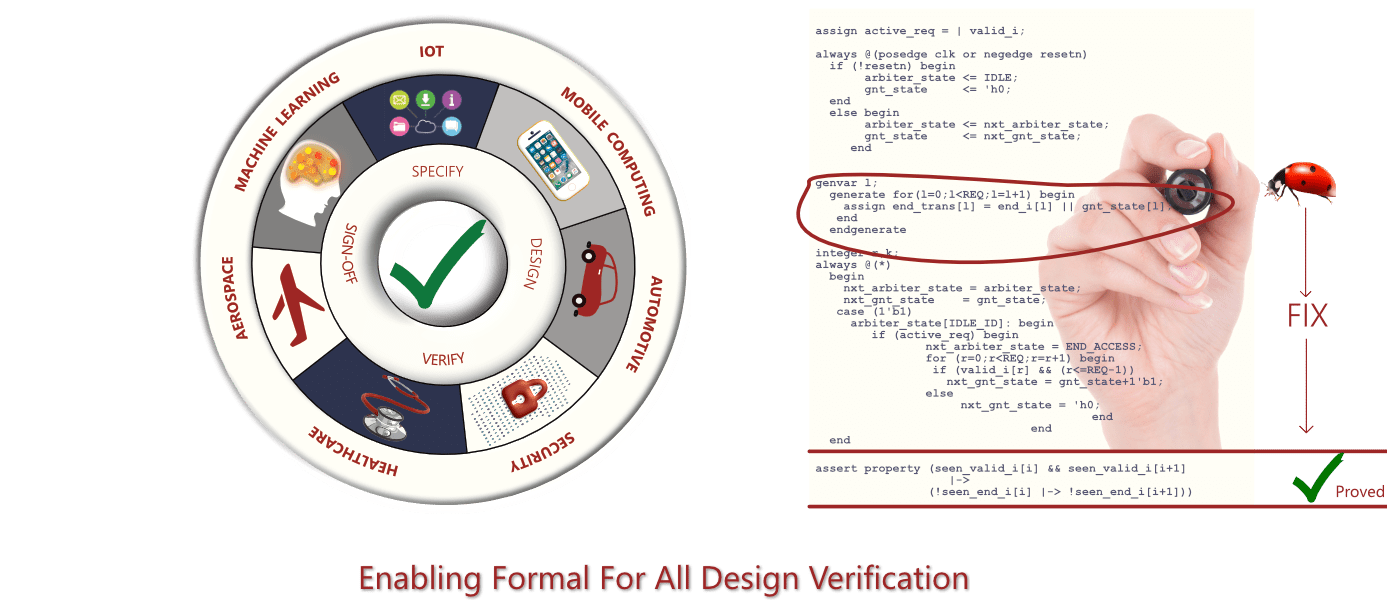

From aerospace, healthcare, and automotive to intelligent AI/ML-powered consumer appliances and industrial process control systems powering up our electrical grids – IC designs are everywhere, and we cannot afford to have failures or defects in these. Whether it is the failure of Ariane 5 or Intel’s FDIV, or the meltdown and spectre security flaws, functional verification of ASICs and FPGAs based on dynamic simulation is struggling.

If you factor in requirements of functional safety and security, conventional simulation-based verification struggles to provide assurance. The only way to guarantee the absence of bugs is via a mathematical proof of correctness, possible only via formal methods.

At Axiomise, our vision is to make formal normal, and for the last six years, we have been doing just that!

We have pioneered the adoption of formal verification in the semiconductor industry since 2017. Led by our visionary CEO, Dr. Ashish Darbari, who has 63 patents in formal verification, and Neil Dunlop an industry veteran with 40 years of experience, Axiomise has helped twenty customers over the last six years by providing them access to bleeding-edge formal verification methodology via its training programmes, consulting & services and vendor-neutral formal verification app for end-to-end verification of RISC-V processors.

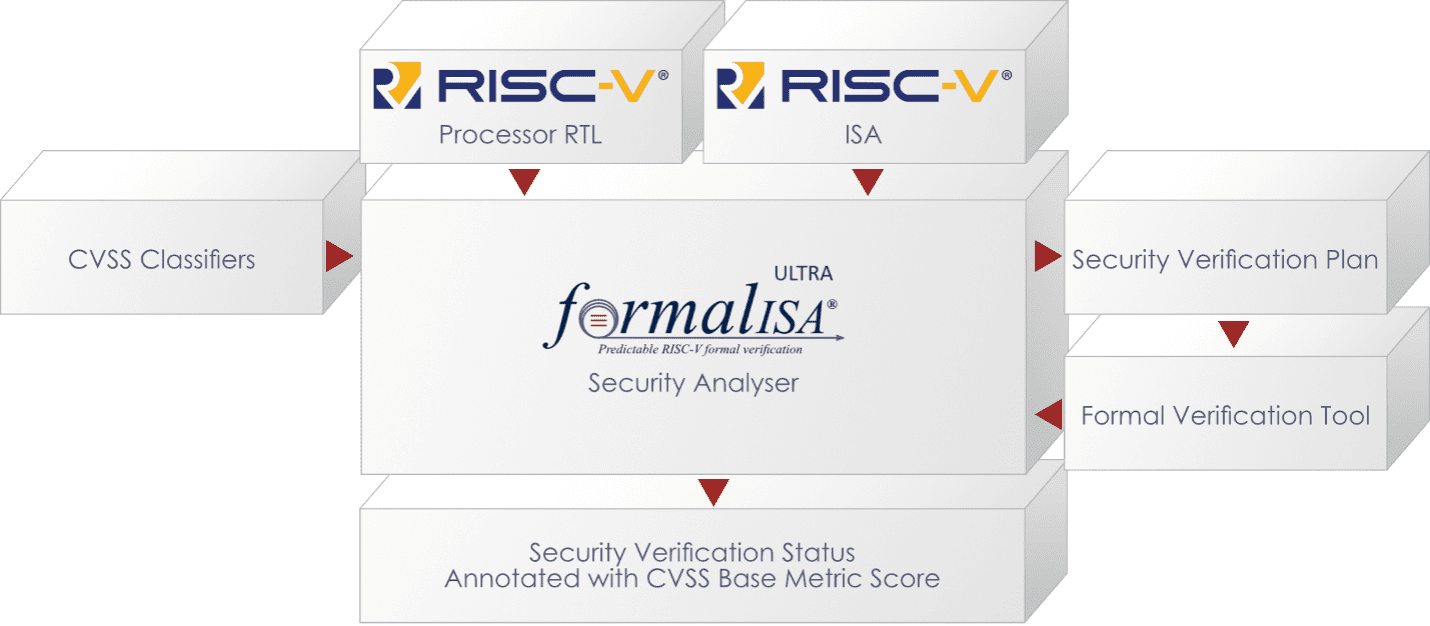

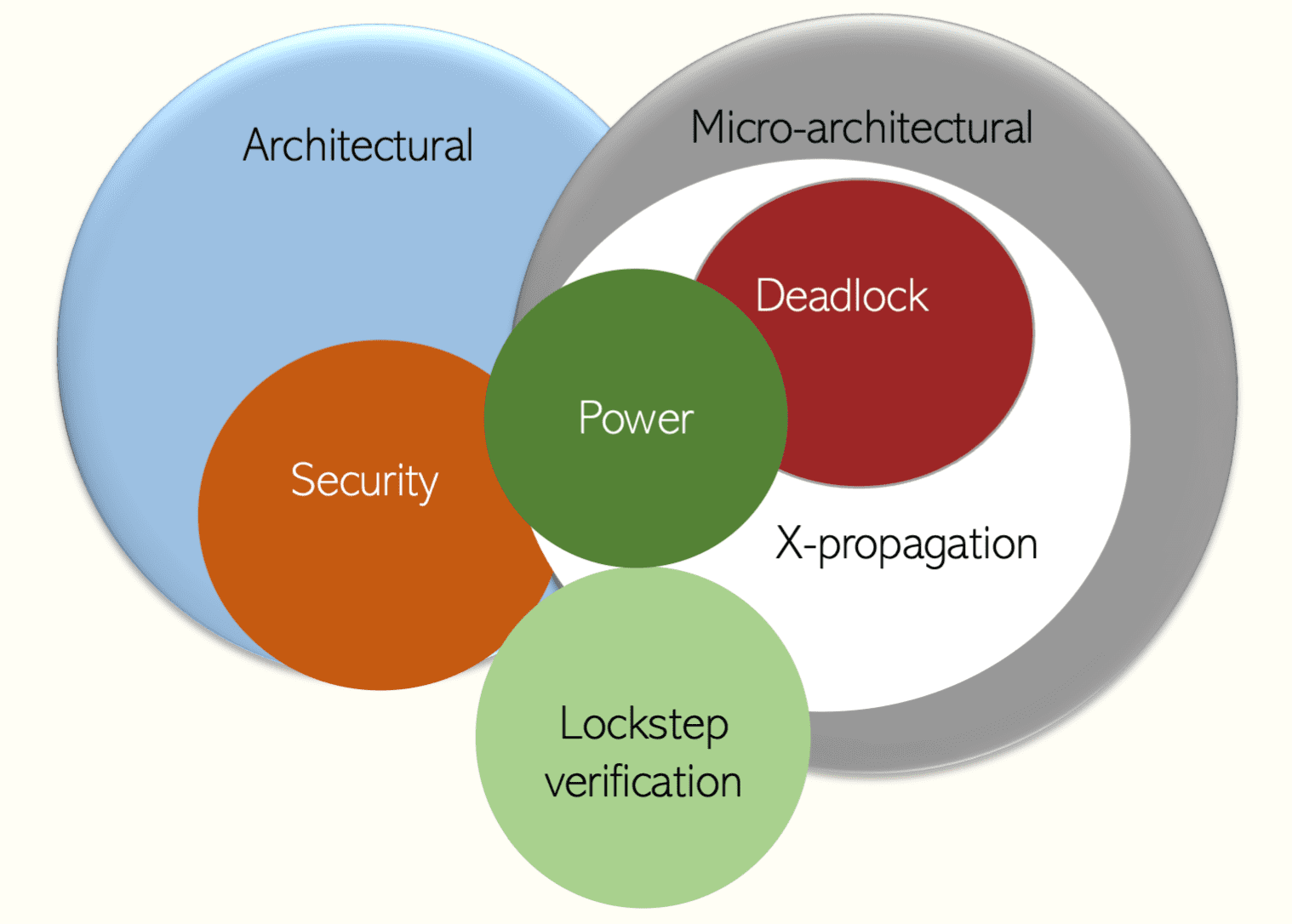

We have made it easier for our customers to deploy formal methods on complex SoCs through our abstraction-driven methodologies and six-dimensional coverage solutions that can be used with any commercial formal verification tool. Axiomise experts can tackle the most challenging formal verification problems on RISC-V, Arm, or x86 processors, GPUs or video blocks, networking blocks including WiFi and 5G, AI/ML hardware, and NoC-based fabrics.

We have helped customers with the usual functional verification challenges but also on safety-critical and security verification tasks finding bugs in previously verified designs and establishing exhaustive proof of bug absence.

The Axiomise Story

Axiomise was founded in 2017 by Dr. Ashish Darbari, who has spent over two decades in the industry and top research labs increasing formal verification adoption. At Axiomise, we believe the only way to make formal methods mainstream for all semiconductor design verification is to enable and empower the end-user of formal – the hundreds of designers and verification engineers in the semiconductor industry. Dr. Darbari was joined by Neil Dunlop in 2022. Between Neil and Ashish, the Axiomise leadership team has over 60 years of formal verification experience on projects – not available anywhere in the world.

We enable formal verification adoption by simplifying the jargon and showing you on your projects how complex problems are easily solved through Axiomise’s abstraction-driven methodologies. Talk to us and find out how our solutions are helping some of the top semiconductor design houses and how we can make formal normal for you and your team. We have helped scores of customers in the last six years on projects and trained over 300 engineers across the industry, besides deploying our automated formal verification app called formalISA to find bugs and build proofs of bug absence.

Learn how to apply formal in a predictable way to achieve high-quality sign-off – we guarantee once you work with us, you will fall in love with formal!

Why Axiomise?

Abstraction-driven, scalable methodologies

Vendor-neutral – our solutions work with any commercial tool

Automated architectural formal verification for RISC-V

SoC formal verification powered by our services

On-demand and instructor-led training programmes

Enabling end-to-end formal sign-off for processors, GPUs, video blocks, networking, AI/ML and more

Executive Team

Chief Executive Officer

Ashish Darbari

As founder & CEO of Axiomise, Dr. Ashish Darbari has led the company to successfully deploy the unique combination of training, consulting, services, and verification IP to various customers. Ashish has expertise in all aspects of formal methods, including theorem proving, property checking, and equivalence checking. Although he has a Doctorate in formal verification from the University of Oxford, to learn formal verification from him, you don’t need a PhD! Some of his former students work at Apple®, Arm®, Blu Wireless®, CERN®, DW Holdings®, Diffblue®, Displaylink®, Meta®, Imagination Technologies®, Infineon®, Intel®, Nokia®, Raytheon®, Rockwell Automation®, Rockley Photonics®, Synopsys®, OneSpin Solutions®, and Xilinx®, to name a few.

Ashish has been actively using formal methods for over two decades. He is one of the foremost authorities in practical applied formal verification, having trained 300 designers and verification engineers worldwide. A keen innovator in formal verification, Ashish has 60+ patents in formal verification. He is also the author of the formalISA® app.

For more information on what people say about us, check out testimonials. Some testimonials that couldn’t make it to the website can be found on [1, 2].

Chief Technology Officer

Neil Dunlop

Neil Dunlop is the chief technology officer (CTO) at Axiomise. Neil is an industry veteran with several decades of experience in the semiconductor industry and exclusively in the field of formal verification for more than 40 years since obtaining an MSc in Computation from the University of Oxford. Neil started his career with assembler programming and micro-code programming before dabbling in the HOL theorem prover. As a formal verification expert with extensive experience using a variety of formal tools, he has worked on hardware design & formal verification at Inmos, STMicroelectronics, ST Ericsson and Imagination Technologies.

Director, Business Development

Laura Long

Laura is the Director of Business Development at Axiomise. She has over 15 years of experience in business development and marketing. She has built strong expertise working with clients and prospective clients with presence and/or residence in various countries of the European Union, in the UK and in the Americas. She has a deep understanding of the cultural differences between these countries besides being fluent in four European languages. Laura started her career as a Marketing Assistant in Uruguay over 20 years ago, moved to London and has lived in the United Kingdom, France, and Italy since then. She holds a graduate degree in International Relations and a degree in Marketing.

Spotlight

Latest News

- Axiomise is a Silver Sponsor at the 2024 edition of DVCon USA, meet the team between 4-7 March 2024 in San Jose

- Laura Long discussed the outlook for 2024 with Daniel Nenni

- Axiomise showcased an excellent Sudoku solver at the Southampton University Careers Fair on 12 February 2024

- The Axiomise team showcased their next-generation formal verification solution at the RISC-V North America Summit in Santa Clara between 7-8 Nov, 2023

- Axiomise presented the tutorial titled: Taking the first steps towards verifying billion gate designs with formal methods in DVCon India, in Bengaluru, between 18-19 Sep, 2023

- The Axiomise team showcased their next-generation formal verification solution at the RISC-V Europe summit in Barcelona between 5-9 June, 2023

- Ashish Darbari gave a talk on how to verify billion-gate NoCs and complex IPs with formal at the ChipEx 2023 event in Tel Aviv on 9 May

- Ashish Darbari talked about how Axiomise is making formal normal in the IoT podcast

- Ashish Darbari presented at the Tenstorrent, RISC-V event “Nerds Talking to Nerds about RISC-V” in Bengaluru, India, on 5 April, 2023

- Laura Long talked to Daniel Nenni in the SemiWiki podcast on the corporate culture of Axiomise

- Axiomise accelerates formal verification adoption

- Ashish Darbari joined an eclectic collection of experts in a DVCon Europe 2022, on the panel on 5G design challenges and their impact on verification

- Ashish Darbari presented at the Cadence Club Formal Event in Bracknell, on 29 Nov 2022

- Ashish Darbari presented at CDNLive 2022 in Munich on 22 Nov

- Axiomise celebrated five years

- Daniel Payne from SemiWiki talks to Ashish Darbari during the 59th DAC

- Ashish Darbari presented a talk: Taming the Beast: RISC-V Formal Verification Made Easy, at the Cadence Design Systems Theatre (DAC Booth #1511) Monday at 4 p.m. and Tuesday at 1:30 p.m.

- Moderated by Brian Bailey, Ashish Darbari joined other industry experts in a pavilion panel at the 59th DAC: Those Darn Bugs! When Will They be Exterminated for Good?

- Ashish Darbari was Amelia Dalton’s guest in her Fish Fry podcast. Find out how Axiomise is making formal verification mainstream?